# Realizing spin qubits in <sup>28</sup>Si/SiGe: heterostructure gating, qubit decoherence and asymmetric charge sensing

## DISSERTATION ZUR ERLANGUNG DES DOKTORGRADES DER NATURWISSENSCHAFTEN (DR. RER. NAT.) DER FAKULTÄT FÜR PHYSIK

### DER UNIVERSITÄT REGENSBURG

vorgelegt von Floyd Schauer aus

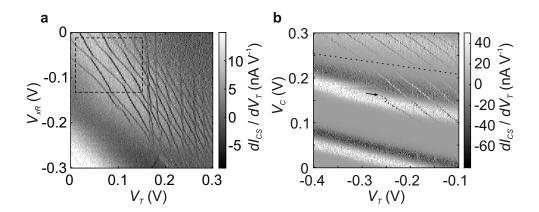

Nürnberg

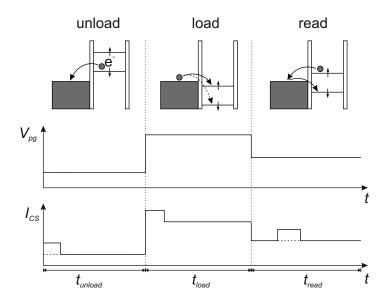

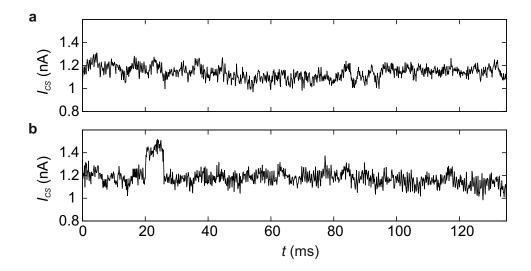

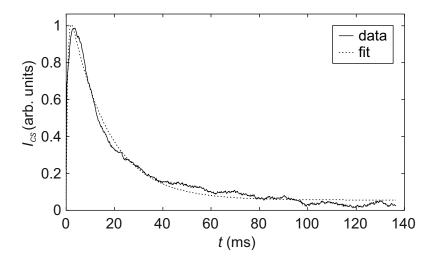

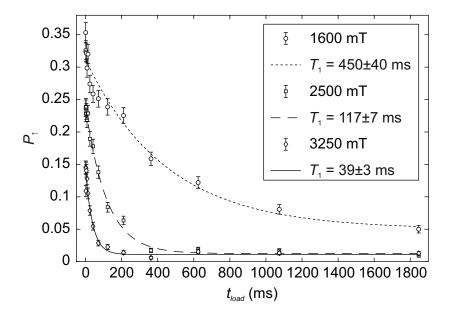

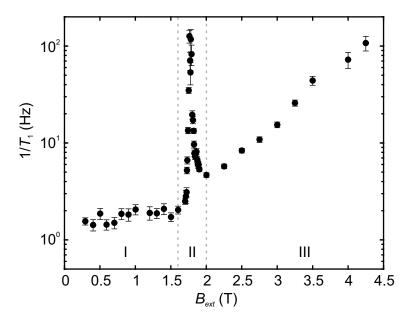

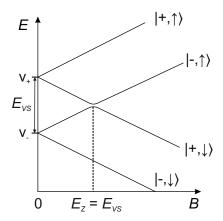

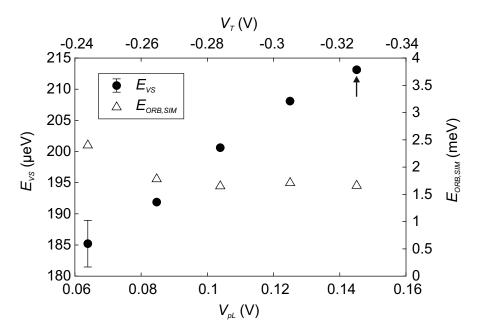

im Jahr 2020

Das Promotionsgesuch wurde eingereicht am 7. Mai 2020. Die Arbeit wurde angeleitet von Prof. Dr. Dominique Bougeard.

# **Contents**

| 1. | Introduction |         |                                                                                                                                         |    |

|----|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2. | Fun          | dament  | tal concepts                                                                                                                            | 5  |

|    | 2.1.         | Silicon | and germanium material system                                                                                                           | 5  |

|    | 2.2.         | Si/SiG  | e heterostructures                                                                                                                      | 7  |

|    | 2.3.         | Magne   | totransport properties of two dimensional electron gases                                                                                | 9  |

|    | 2.4.         | Quant   | um dots in Si/SiGe                                                                                                                      | 10 |

|    |              | 2.4.1.  | Coulomb blockade                                                                                                                        | 12 |

|    |              | 2.4.2.  | Coulomb diamonds                                                                                                                        | 13 |

|    | 2.5.         | Double  | e quantum dots                                                                                                                          | 15 |

|    | 2.6.         | Single  | electron in magnetic field                                                                                                              | 17 |

|    | 2.7.         | Electri | c dipole spin resonance using a magnetic field gradient                                                                                 | 18 |

| 3. | Gati         | ng of u | indoped Si/SiGe 2DEG                                                                                                                    | 21 |

|    | 3.1.         | Growt   | h and semiconductor layer structure                                                                                                     | 21 |

|    |              | 3.1.1.  | Molecular beam epitaxy                                                                                                                  | 21 |

|    |              | 3.1.2.  | Post-growth processing                                                                                                                  | 23 |

|    | 3.2.         | Hall m  | easurement                                                                                                                              | 24 |

|    |              | 3.2.1.  | Hall bar sample layout                                                                                                                  | 24 |

|    |              | 3.2.2.  | Accumulation of charge carriers in undoped Si/SiGe                                                                                      | 26 |

|    |              | 3.2.3.  | Magnetotransport characterization                                                                                                       | 26 |

|    | 3.3.         | Introd  | uction to the gating regimes of undoped Si/SiGe                                                                                         | 28 |

|    | 3.4.         | Biased  | ${\rm cool\text{-}down} \ \dots $ | 33 |

|    |              | 3.4.1.  | Shift of the threshold voltage and density                                                                                              | 33 |

|    |              | 3.4.2.  | Effect of biased cool-down on the mobility                                                                                              | 37 |

|    | 3.5.         | Illumir | nation                                                                                                                                  | 38 |

|    |              | 3.5.1.  | Resetting the charge configuration                                                                                                      | 38 |

|    |              | 3.5.2.  | Illumination model of undoped Si/SiGe                                                                                                   | 40 |

|    |              | 3.5.3.  | Effect of illumination on mobility                                                                                                      | 42 |

|    | 3.6          | Conclu  | ision                                                                                                                                   | 45 |

| 4. | Tun  | ing of a   | a single quantum dot to the last electron regime             | 4 |

|----|------|------------|--------------------------------------------------------------|---|

|    | 4.1. | Device     | e layout and fabrication                                     | 4 |

|    |      | 4.1.1.     | Improvements to the gate design                              | 4 |

|    |      | 4.1.2.     | Robust fabrication of the depletion gate layer               | 4 |

|    | 4.2. | Charg      | e sensor optimization                                        | 5 |

|    |      | 4.2.1.     | Initial sensor characterization                              | 5 |

|    |      | 4.2.2.     | A different charge sensor configuration                      | ţ |

|    | 4.3. | Deplet     | tion to the last electron                                    | ţ |

|    |      | 4.3.1.     | Initial qubit dot region characterization                    | ţ |

|    |      | 4.3.2.     | Suppressing unintentional quantum dots and the last electron | ţ |

|    | 4.4. | Concl      | usion                                                        | ٦ |

| 5. | Rela | axation    | study on single electron spins                               | 5 |

|    |      |            | y selective spin readout                                     | ŗ |

|    |      | 5.1.1.     | Spin-to-charge conversion                                    | ! |

|    |      | 5.1.2.     | Spin-up and -down signal                                     |   |

|    |      | 5.1.3.     | Measurement of the tunnel barriers                           |   |

|    | 5.2. | $T_1$ rela | axation study                                                |   |

|    |      | 5.2.1.     |                                                              |   |

|    |      | 5.2.2.     | $T_1(B)$ spectroscopy and valley hotspot                     |   |

|    | 5.3. | Valley     | splitting across multiple gate voltage configurations        |   |

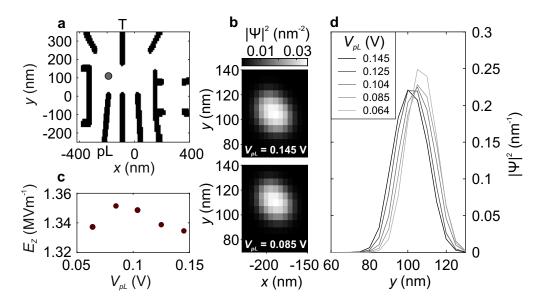

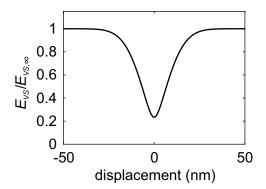

|    |      | 5.3.1.     | Self-consistent Schrödinger-Poisson simulations              |   |

|    |      | 5.3.2.     | Orbital splitting                                            |   |

|    |      | 5.3.3.     | Valley splitting in proximity to a monolayer step            |   |

|    | 5.4. | Conclu     | usion                                                        |   |

| 6. | Sing | gle spir   | n manipulation in <sup>28</sup> Si/SiGe                      | • |

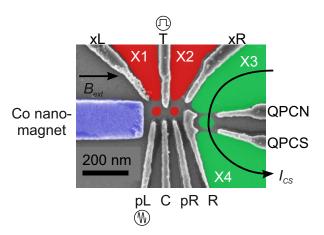

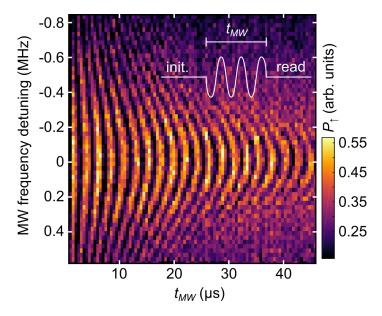

|    | 6.1. | Spin n     | nanipulation by electric dipole spin resonance               | , |

|    |      | 6.1.1.     | Rabi oscillation measurement                                 | , |

|    | 6.2. | Depha      | using time $T_2^*$                                           | , |

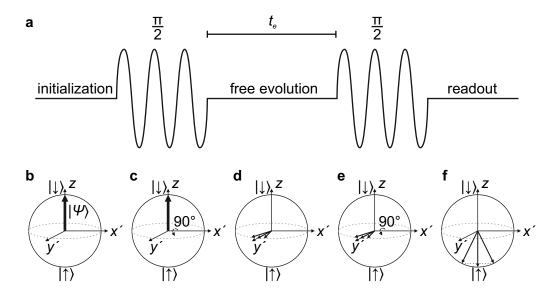

|    |      | 6.2.1.     | Accessing dephasing with the Ramsey pulse scheme             |   |

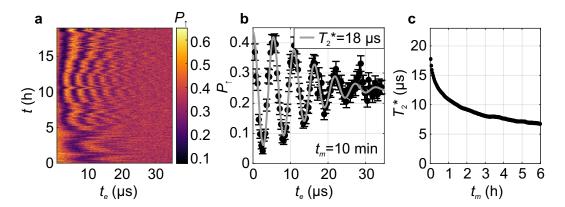

|    |      | 6.2.2.     | Ramsey fringe measurement                                    |   |

|    |      | 6.2.3.     | Extracting $T_2^*$ dependent on measurement time             |   |

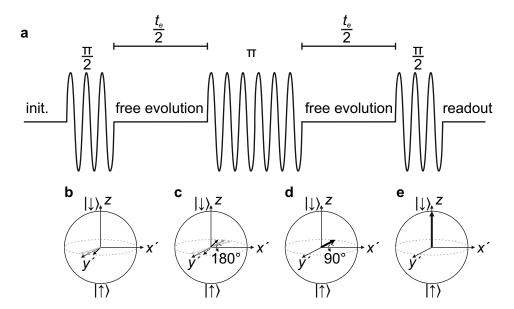

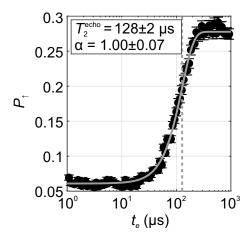

|    | 6.3. | Refoci     | using slow noise by Hahn echo                                |   |

|    | 6.4  | Concl      | usion                                                        |   |

| 7.  | Asy        | mmetric sensing dot                                             | 83  |  |  |  |  |

|-----|------------|-----------------------------------------------------------------|-----|--|--|--|--|

|     | 7.1.       | Concept of a new kind of charge sensor                          | 83  |  |  |  |  |

|     |            | 7.1.1. Enhancement of signal-to-noise with a transistor         | 83  |  |  |  |  |

|     |            | 7.1.2. Conventional quantum dot charge sensor                   | 84  |  |  |  |  |

|     |            | 7.1.3. Increasing the voltage swing                             | 86  |  |  |  |  |

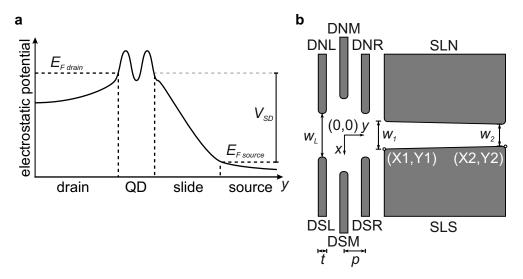

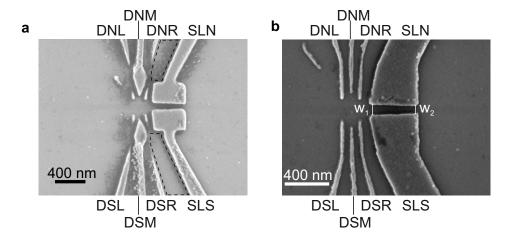

|     | 7.2.       | Device layout and engineering of the electrostatic potential    | 86  |  |  |  |  |

|     |            | 7.2.1. Decreasing capacitive coupling                           | 86  |  |  |  |  |

|     |            | 7.2.2. Fabrication optimization                                 | 88  |  |  |  |  |

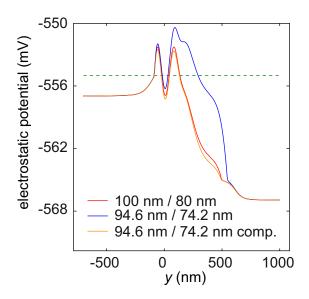

|     |            | 7.2.3. Feedback to the simulation                               | 90  |  |  |  |  |

|     | 7.3.       | Instabilities in asymmetric sensing dot (ASD) devices           | 92  |  |  |  |  |

|     | 7.4.       | Asymmetric Coulomb diamonds                                     | 93  |  |  |  |  |

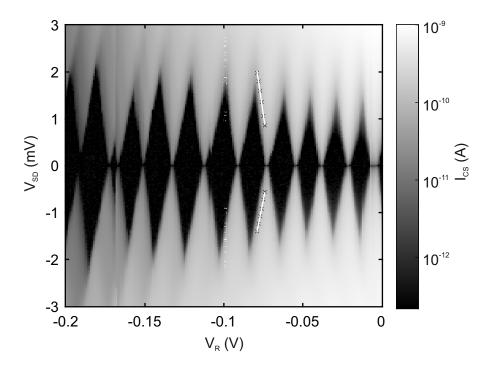

|     |            | 7.4.1. Proof of concept by slide gate variation                 | 94  |  |  |  |  |

|     |            | 7.4.2. Slide potential variation                                | 98  |  |  |  |  |

|     | 7.5.       | Conclusion and outlook                                          | 99  |  |  |  |  |

| 8.  | Con        | aclusion and Outlook                                            | 101 |  |  |  |  |

| Α.  | . Appendix |                                                                 |     |  |  |  |  |

|     |            | Determination of source lever arm of conventional charge sensor | 105 |  |  |  |  |

|     | A.2.       | Measurement setup information                                   | 106 |  |  |  |  |

|     |            | A.2.1. He dewar with magnet insert                              | 106 |  |  |  |  |

|     |            | A.2.2. Dilution refrigerator setup                              | 106 |  |  |  |  |

|     |            | A.2.3. <sup>3</sup> He-cryostat                                 | 106 |  |  |  |  |

|     | A.3.       | Simulation details                                              | 107 |  |  |  |  |

|     | A.4.       | Details on the fabrication                                      | 107 |  |  |  |  |

|     |            | A.4.1. Hall bar samples                                         | 107 |  |  |  |  |

|     |            | A.4.2. DQD and ASD devices                                      | 108 |  |  |  |  |

|     |            | A.4.3. Optical lithography recipe                               | 109 |  |  |  |  |

|     |            | A.4.4. Gate lines with LOR3A resist                             | 110 |  |  |  |  |

|     |            | A.4.5. Lift-off procedure                                       | 111 |  |  |  |  |

|     |            | A.4.6. Etching recipe                                           | 112 |  |  |  |  |

|     |            | A.4.7. Metallization recipe                                     | 112 |  |  |  |  |

|     |            | A.4.8. Atomic layer deposition recipe                           | 113 |  |  |  |  |

|     |            | A.4.9. Electron beam lithography recipe                         | 113 |  |  |  |  |

| Bil | bliog      | raphy                                                           | 117 |  |  |  |  |

| $\sim$ |    |    |    |    |

|--------|----|----|----|----|

| Co     | nı | -0 | n1 | .5 |

| Acronyms        | 127 |

|-----------------|-----|

| Acknowledgments | 129 |

## 1. Introduction

Since the advent of computing, this technology has brought substantial economic growth and scientific discoveries. This success is based on the ability for computers to solve some kinds of problems faster than humans. However, there is still a class of intractable problems that is hard to solve for classical computers, meaning that the computing time and memory scale exponentially with the problem size [1]. A new kind of computer, harnessing the quantum superposition and entanglement for computation, should be able to solve some of these problems in polynomial time [1, 2]. Such a universal quantum computer is proven to solve problems such as prime factorization, finding discrete logarithms, solving linear systems of equations and searching unsorted data faster than its classical counterpart for large problem sizes [3–6]. Apart from these applications, a quantum computer is predicted to be highly efficient in simulating physical systems governed by quantum mechanics, offering insights which would be hard to obtain in the real system [7–10]. For example, the development of drugs could be sped up by quantum simulation [11].

The fundamental building block of a quantum computer is the qubit: a two-level quantum system allowing the superposition of the levels as well as the entanglement between multiple qubits. Qubits can be realized in a multitude of physical systems including photons, trapped ions and superconducting circuits [12–15].

The field of quantum computing is currently in a stage of noisy intermediate-scale quantum technology, where around 50 noisy qubits have been demonstrated in a single device [16, 17]. Although quantum supremacy, the point where it takes longer to calculate a specific algorithm in a classical supercomputer than on a quantum computer, is claimed to be surpassed [17], there is still a long way to go for the realization of a fault tolerant universal quantum computer [18, 19]. Especially the large number of physical qubits expected to be required for the implementation of one logical, meaning error-corrected, qubit imply that scalable qubit implementations have to be developed for progress in fault-tolerant quantum computing.

A particularly promising approach is the implementation of spin qubits in gatedefined semiconductor nanostructures due to the existing highly scalable manufacturing techniques and the good tunability of the confinement potential [20]. Most of the preliminary work in this branch of quantum computing research was done in GaAs, building on advancements in quantum-transport-, Coulomb-blockade- and spin-blockade-physics [21]. Yet, the strong fluctuating Overhauser field of the host nuclei and the strong spin-orbit coupling strength were limiting the qubit coherence with dephasing times in the order of 10 ns [22–24].

By moving to silicon as the basis for gate-defined quantum dots, with only 4.685 % of the nuclear spin carrying isotope <sup>29</sup>Si in the natural Si composition and a weak spin-orbit interaction, the interaction of the spin with its environment is reduced [25–32]. The isotopical purification of <sup>28</sup>Si allows to engineer a virtually nuclear-spin-free host material [33–35]. These improvements yielded remarkable dephasing times in the order of 120 µs in metal oxide semiconductor (MOS) structures [31] and 20 µs for electron spin qubits in <sup>28</sup>Si/SiGe heterostructures [36, 37] with control-fidelities surpassing 99.9 % [36].

In our group, we have developed a qubit platform based on gate-defined quantum dots (QDs) in <sup>28</sup>Si/SiGe heterostructures in previous work [38–40]. The heterostructures intended for qubit experiments feature a quantum well (QW) which is grown by means of molecular beam epitaxy (MBE) using an isotopically purified <sup>28</sup>Si source crystal with only 60 ppm of remaining <sup>29</sup>Si. Combining this MBE-grown heterostructure with a magnet placed in the plane of the QD-defining gate layer, we have a unique framework for qubit realization in a collaborative effort with the group of Lars Schreiber at the RWTH Aachen. Previous work demonstrated single electron operation in our qubit platform.

In this thesis we set out to deepen our understanding of the heterostructure properties to reach high-yield single electron tuning, since for example charge reconfigurations in defect trap states impede the device tuning. In parallel, a demonstration of qubit operation and with this a measurement of qubit characteristics such as relaxation and dephasing times remained as the aim of this thesis.

The current research in quantum computing is moving towards qubit operation at temperatures around 1 K where more cooling power is available in the refrigerators, in an effort towards the integration of control electronics in vicinity of the qubits [41]. Signal-to-noise ratio (SNR) and bandwidth plays an important role for a robust and fast measurement of the spin, especially at elevated temperatures [42]. A new kind of charge sensor, presented in the last part of this thesis, is a promising candidate to deliver these features.

This thesis is organized as follows:

- In chapter 2 we will discuss the fundamental theoretical concepts required for a basic understanding of the experimental studies presented in this thesis.

- In chapter 3 we will present a characterization of the gated undoped Si/SiGe heterostructures building the basis for our nanostructure devices.

- In chapter 4 we will show the initial tuning of a single quantum dot with an adjacent charge sensor in <sup>28</sup>Si/SiGe.

- In chapter 5 we will demonstrate the spin-to-charge conversion and study the spin relaxation in order to extract the valley splitting in our qubit device.

- In chapter 6 we will introduce the spin manipulation via electric dipole spin resonance (EDSR) and access the dephasing and decoherence times in our qubit.

- In chapter 7 we will study a concept for a new kind of charge sensor aiming towards a large SNR and high bandwidth spin readout.

# 2. Fundamental concepts

In this chapter, we will discuss the underlying concepts required for an understanding of the experiments studied in this thesis.

#### 2.1. Silicon and germanium material system

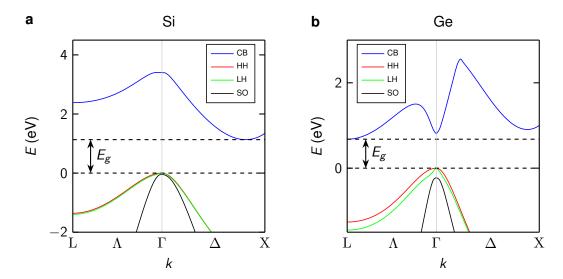

The devices studied in this thesis are based on Si/SiGe QW-heterostructures. Therefore, we first turn towards the properties of this material system. Fig. 2.1 shows the simulated band structure of silicon (a) and germanium (b). Both materials are indirect semiconductors, which manifests in a conduction band minimum that is not at the  $\Gamma$ -point of the Brillouin . The band gaps of Si and Ge have been determined to 1.12 eV and 0.661 eV, respectively [43, 44]. Both elements crystallize in a diamond lattice with lattice constants of  $a_{\rm Si} = 543.1\,\mathrm{pm}$  for silicon and  $a_{\rm Ge} = 565.8\,\mathrm{pm}$  for germanium [43, 44]. The two elements are miscible into the alloy  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  with any desired Ge content x. The resulting lattice constant  $a_0(x)$  of the  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  is described by Vegard's law [45]

$$a_0(x) = a_{Si}(1-x) + a_{Ge}x.$$

(2.1)

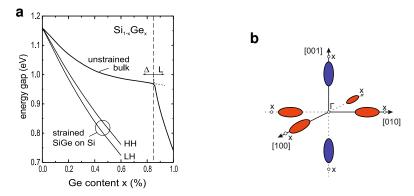

Fig. 2.2 a shows the band gap for relaxed  $Si_{1-x}Ge_x$  bulk material with a monotonous decrease in band gap for increasing Ge content x. Despite of the larger band gap of pure Si compared to any  $Si_{1-x}Ge_x$  alloy, it is possible to engineer a Si-QW heterostructure.

Figure 2.1. – a The band structure of silicon with the conduction (blue), heavy-hole (red), light-hole (green) and split-off (black) bands. The indirect band gap of Si with  $E_g = 1.12 \,\mathrm{eV}$ . b The band structure of germanium with an indirect band gap of  $E_g = 0.661 \,\mathrm{eV}$ . Simulated with [46]. Adapted from [47].

Figure 2.2. – a The band gap of unstrained  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  as a function of the Ge content x is shown in the upper line. The nature of the band gap is Si-like with the conduction band minimum lying in the  $\Delta$ -direction for x < 0.85 and Ge-like with the conduction band minimum located at the L point of the Brillouin zone for x > 0.85. The lower lines cover strained  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  which is not covered in this thesis. Republished with permission of IOP Publishing, Ltd and AIP Publishing, from [48, 49]; permission conveyed through Copyright Clearance Center, Inc. b The surfaces of constant energy close to the conduction band minima in the Si Brillouin zone forming ellipsoids. In the case of biaxial tensile strain applied to bulk Si in the [100] and [010] directions, the ellipsoids in the [001] direction (shown in blue) are shifted lower in energy, while the ellipsoids in the [100] and [010] directions are shifted up in energy.

### 2.2. Si/SiGe heterostructures

When Si is grown onto a relaxed  $Si_{1-x}Ge_x$  substrate, the Si lattice adapts to the larger SiGe lattice constant, introducing strain in the Si layer. This strain lifts the sixfold valley degeneracy present in bulk Si, as depicted in Fig. 2.2 b. The twofold degenerate  $\Delta_2$  valleys are shifted down in energy and the fourfold degenerate  $\Delta_4$  valleys are shifted up in energy in the strained Si. Furthermore, the twofold ground state degeneracy is lifted by the QW confinement potential leading to the valley splitting  $E_{VS}$  [50]. The band gap of the strained Si gets reduced, which leads to a type-II band alignment in a Si/Si<sub>1-x</sub>Ge<sub>x</sub> QW heterostructure [39].

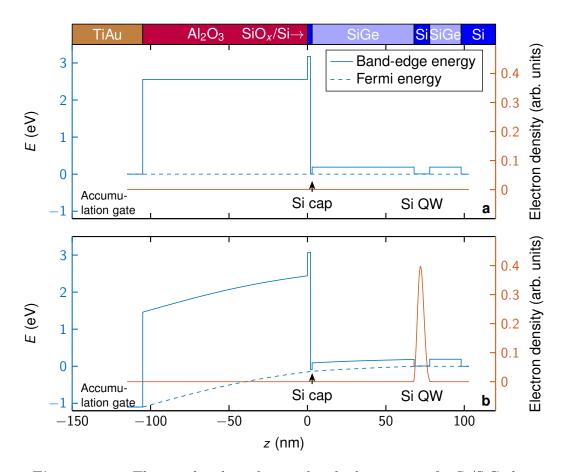

Fig. 2.3 a shows the simulated conduction band edge energy as a function of the coordinate in growth direction z in an undoped Si/SiGe QW heterostructure. Due to the absence of doping, the band edge energy is flat with steps due to differences in the material composition. The Si QW as well as the Si cap represent a minima of the conduction band edge energy. In this flat-band condition the first subband in the QW is above the Fermi energy indicated by the dashed line and no electrons are allowed to enter the QW, indicated by the zero electron density in Fig. 2.3 a. Therefore, it is mandatory to add a gate oxide and a metal layer further referred to as accumulation gate, located at z < 0 nm, in order to manipulate the band edge energy. A positive voltage applied to the TiAu accumulation gate lowers the band edge energy, as shown in Fig. 2.3 b, eventually leading to the first subband energy in the QW shifting below the Fermi energy. This allows electrons to enter the QW, indicated by the non-zero electron density in the QW region. When only the first subband is occupied, the electrons form a two dimensional electron gas (2DEG). Note that no electron density is predicted to accumulate in the 1 nm Si cap, as the larger confinement energy contribution keeps the first subband energy above the Fermi energy. The 2DEG can be characterized by magnetotransport studies, which will be covered in the following section.

Figure 2.3. – The simulated conduction band edge energy of a Si/SiGe heterostructure with an  $Al_2O_3$  gate oxide and a metal accumulation gate as a function of the coordinate z oriented along the growth direction (blue). The simulated electron density as a function of z is plotted in orange. a The flat band structure in the case of 0 V applied to the accumulation gate with respect to the grounded QW. As the first subband in the QW is above the Fermi energy, no charge carriers are allowed in the QW resulting in zero electron density. b Here, 1.1 V is applied to the accumulation gate, resulting in a band bending which induces a non-zero charge carrier density in the QW as the first subband moves below the Fermi energy. Adapted from [47].

# 2.3. Magnetotransport properties of two dimensional electron gases

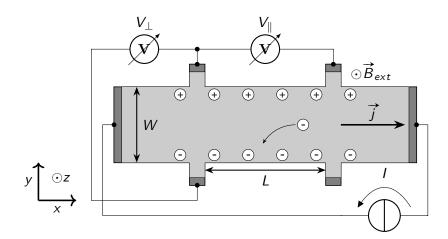

A 2DEG patterned in a Hall bar geometry is schematically depicted in Fig. 2.4, with the ohmic contacts indicated by the dark gray regions. A typical magnetotransport measurement accesses the longitudinal and transversal resistivities  $\rho_{xx}$  and  $\rho_{xy}$  in a four-point measurement of the longitudinal and transversal resistance  $V_{\parallel}/I$  and  $V_{\perp}/I$ , respectively and the consideration of the Hall bar width and length dimensions:

$$\rho_{xx} = \frac{V_{\parallel}}{I} \frac{W}{L} \tag{2.2}$$

$$\rho_{xy} = \frac{V_{\perp}}{I}.\tag{2.3}$$

The out-of-plane magnetic field  $B_{ext}$  is varied and due to the Lorentz-force acting upon the moving charge carriers, a non-zero Hall resistance is detected. In the regime described by the classical Hall effect [51],  $V_{\perp}$  rises linearly with the magnetic field while  $V_{\parallel}$  stays constant. The resulting longitudinal and transversal resistivities are described by

$$\rho_{xx} = \frac{m^*}{ne^2\tau} = \frac{1}{ne\mu} \quad \text{and} \tag{2.4}$$

$$\rho_{xy} = \frac{B_{ext}}{en},\tag{2.5}$$

where  $m^*$  is the effective mass of the charge carriers, e is the elementary charge, n is the charge carrier density,  $\tau$  is the mean scattering time and  $\mu = \frac{e\tau}{m^*}$  is the charge carrier mobility [52].

The Fermi wave vector is then described by

$$k_F = \sqrt{\frac{4\pi n}{g_s g_v}},\tag{2.6}$$

with  $g_s$  and  $g_v$  being the spin and valley degeneracies, respectively. The Fermi velocity  $v_F$  and the mean free path l are obtained as

$$v_F = \frac{\hbar k_F}{m^*} \quad \text{and} \tag{2.7}$$

$$l = v_F \tau = -\frac{\hbar}{e} \mu \sqrt{\pi n}. \tag{2.8}$$

The mean free path l is a measure for the average length the charge carriers travel between two scattering events.

By confining the 2DEG in the two in-plane dimensions, it is possible to create QDs in the Si host material. We will discuss the characteristic properties of these systems in the following section.

Figure 2.4. – A schematic illustration of a Hall bar sample with width W and segment length L. A current density  $\vec{j}$  is injected in the x direction. The external magnetic field  $\vec{B}_{ext}$  is oriented along the z direction, leading to a deflection of the electrons due to the Lorentz force. Charges accumulate on the edges of the sample, inducing a non-zero transversal voltage  $V_{\perp}$ .

#### 2.4. Quantum dots in Si/SiGe

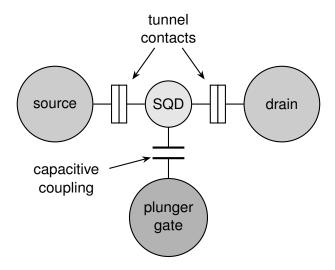

An island formed in the 2DEG due to lateral confinement, commonly referred to as single quantum dot (SQD), coupled to the source and drain reservoirs via tunnel contacts is illustrated in Fig. 2.5. A plunger gate is capacitively coupled to the SQD. This structure is commonly approximated by a circular disc in the 2DEG with a radius r and an electron charge of -eN for N electrons occupying the SQD. The self-capacitance of this disc is described by

$$C = 8\epsilon\epsilon_0 r,\tag{2.9}$$

with  $\epsilon$  being the dielectric constant of the surrounding material, which is assumed to be homogeneous in this approximation, and the vacuum permittivity  $\epsilon_0$  [52]. The

electrostatic energy of the island is then given by

$$E_{\text{elstat}}(N) = \frac{e^2 N^2}{2C} = \frac{e^2 N^2}{16\epsilon\epsilon_0 r}.$$

(2.10)

The energy required to add the (N + 1)-th onto a SQD occupied with N electrons is the difference between the electrostatic energies

$$E_c(N+1) = E_{\text{elstat}}(N+1) - E_{\text{elstat}}(N) = \frac{e^2}{C} \left( N + \frac{1}{2} \right) \stackrel{N \gg 1}{\approx} \frac{e^2}{C} N = \frac{e^2}{8\epsilon \epsilon_0 r} N.$$

(2.11)

However, the term charging energy is commonly used for

$$\Delta E_c = E_c(N+1) - E_c(N) = \frac{e^2}{C} = \frac{e^2}{8\epsilon\epsilon_0 r}.$$

(2.12)

For a SQD with a radius of 50 nm and  $\epsilon = 11.7$  of Si this characteristic energy scale is  $\Delta E_c \approx 3.9$  meV, which corresponds to a temperature of 45 K.

The single-particle level spacing can be approximated using the model of a quantum mechanical harmonic oscillator [52]

$$\Delta = \hbar\omega_0 = \frac{\hbar^2}{4m^*r^2}. (2.13)$$

For a SQD in Si with  $m^* = 0.19 \, m_e$  and a radius of 50 nm, this energy scale computes to 40  $\mu$ eV or a temperature of 0.5 K. This is two orders of magnitude smaller than  $\Delta E_c$  indicating that the total energy of the SQD is governed by the Coulomb interaction energy for the laterally defined SQDs studied in this thesis.

Considering the capacitively coupled plunger gate shown in Fig. 2.5, the ground state energy for a SQD occupied with N electrons depends on the plunger gate voltage  $V_{pg}$

$$E_N(V_{pg}) = E_N(V_{pg}^0) - eN\alpha_{pg}(V_{pg} - V_{pg}^0),$$

(2.14)

for small ranges around a fixed  $V_{pg}^0$  with  $\alpha_{pg} = \frac{C_{pg}}{C}$  being the lever arm describing the ratio of the capacitive coupling  $C_{pg}$  of the plunger gate to the SQD to the self-capacitance C [52]. For a SQD with initially N-1 electrons we define the electrochemical potential for increasing the electron occupation to N as

$$\mu_N(V_{pg}) = E_N(V_{pg}) - E_{N-1}(V_{pg}). \tag{2.15}$$

**Figure 2.5.** – A schematic depiction of a SQD with tunnel contacts to source and drain reservoirs. The plunger gate couples capacitively onto the SQD.

#### 2.4.1. Coulomb blockade

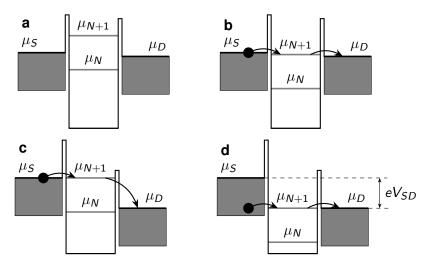

Fig. 2.6 shows a schematic representation of the energetic situation for a SQD in between source and drain reservoirs. The electronic levels in the source and drain reservoirs are filled up to the electrochemical potentials  $\mu_S$  and  $\mu_D$ , respectively, in the case of low temperatures. We first consider the situation where only a small bias voltage is applied between the reservoirs. In Fig. 2.6 a the SQD is occupied with N electrons, as  $\mu_N < \mu_D < \mu_S$ . However, the energy required to add the (N+1)-th electron onto the SQD is not available, as  $\mu_{N+1} > \mu_S > \mu_D$ . This leads to a constant occupation of the SQD with the same N electrons, which effectively blocks the current flowing between the source and drain reservoirs. This situation is commonly termed Coulomb blockade since the Coulomb interaction prevents a (N+1)-th electron to enter the SQD. Using the plunger gate voltage, combining Eqs. 2.14 and 2.15 the electrostatic potential can be tuned with

$$\mu_N(V_{pg}) = \mu_N(V_{pg}^0) - e\alpha_{pg}(V_{pg} - V_{pg}^0). \tag{2.16}$$

Fig. 2.6 b shows the situation where Coulomb blockade is lifted, by tuning  $\mu_{N+1}$  to a value in between  $\mu_S$  and  $\mu_D$  by a change of  $V_{pg}$ . In this situation either N+1 or N electrons can occupy the SQD, allowing for sequential transport of electrons through the SQD, indicated by the arrows in Fig. 2.6 b.

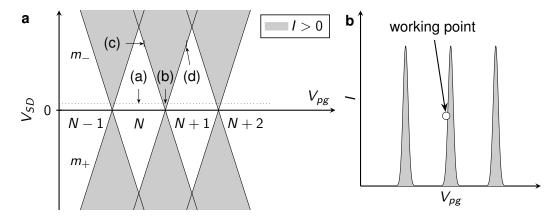

#### 2.4.2. Coulomb diamonds

Considering the current through the SQD as a function of the bias voltage  $V_{SD}$  and  $V_{pg}$ , we expect the regions of suppressed current to form diamond shaped regions, as depicted in Fig. 2.7a. The grey regions mark a transport current through the SQD. The borders of the blockade regions, commonly referred to as Coulomb diamonds, mark the configurations of  $V_{SD}$  and  $V_{pg}$  where either of the reservoir chemical potentials is aligned with a SQD chemical potential, as schematically depicted in Fig. 2.6 c for  $\mu_S = \mu_{N+1}$  and Fig. 2.6 d for  $\mu_D = \mu_{N+1}$ . We mark the configurations in Fig. 2.7a with the labels corresponding to the subfigures in Fig. 2.6.

Figure 2.6. – A schematic illustration of the electrochemical potentials in a SQD occupied with N electrons with small (a, b) and large (c, d) source-drain bias voltages. **a** There are no energy levels in the QD lying in between the electrochemical potentials of source and drain  $\mu_S$  and  $\mu_D$ . The system is considered to be in Coulomb blockade as no electron transport is allowed. **b** The level  $\mu_{N+1}$  lies in the source-drain bias window and sequential tunneling of electrons is allowed. **c**  $\mu_{N+1}$  is aligned with  $\mu_S$  and transport is allowed. **d**  $\mu_{N+1}$  is equal to  $\mu_D$  and current is allowed to flow. The difference in the source and drain electrochemical potentials  $eV_{SD}$  is indicated on the right hand side.

In the following, we consider the case where the drain reservoir is grounded while the bias voltage is applied to the source reservoir. So far we only took the capacitive coupling of the plunger gate into account, but also the reservoirs are coupled capacitively to the SQD. The negatively sloped diamond borders, labeled  $m_{-}$  in Fig. 2.7 a, satisfy

$$\Delta\mu_N = \mu_D = 0, \tag{2.17}$$

meaning that the capacitive coupling of the source reservoir and the plunger gate keeps the SQD electrostatic potential aligned with the potential of the grounded drain reservoir. The shift in  $\mu_N$  in response to changes of  $\Delta V_{SD}$  and  $\Delta V_{pg}$  can be described by

$$\Delta \mu_N = -e\Delta V_{SD} \frac{C_S}{C} \text{ and}$$

(2.18)

$$\Delta\mu_N = +e\Delta V_{pg} \frac{C_{pg}}{C}.$$

(2.19)

Here,  $C_S$  describes the capacitive coupling of the source reservoir onto the SQD. Dividing Eq. 2.18 by Eq. 2.19, we get an equation for the negative slope  $m_-$  of the diamond borders described by Eq. 2.17

$$m_{-} = \frac{\Delta V_{SD}}{\Delta V_{pg}} = -\frac{C_{pg}}{C_S} = -\frac{\alpha_{pg}}{\alpha_S} \tag{2.20}$$

with the source lever arm

$$\alpha_S = \frac{C_S}{C}.\tag{2.21}$$

In a similar fashion we can derive the slope of the positively sloped diamond borders

$$m_{+} = \frac{C_{pg}}{C - C_{S}}. (2.22)$$

Inserting Eqs. 2.20 and 2.22 in Eq. 2.21, we can express the source lever arm as a function of the negative  $(m_{-})$  and positive  $(m_{+})$  diamond border slopes

$$\alpha_S = \frac{m_+}{m_+ - m_-} \stackrel{m_+ > 0; \ m_- < 0}{=} \frac{|m_+|}{|m_+| + |m_-|}.$$

(2.23)

Fig. 2.7 b shows the current I through the SQD as a function of  $V_{pg}$  for a small fixed  $V_{SD}$  indicated by the dotted line in Fig. 2.7 a. Peaks in I are expected when the Coulomb blockade is lifted. On each side of the peaks,  $dI/dV_{pg}$  is large, yielding a large change in I for a small change in  $V_{pg}$ . In the same way the current signal is sensitive to changes in  $V_{pg}$ , it is also sensitive to any other changes to the electrostatic potential. An electron entering or leaving a nearby QD may induce such a change in

the electrostatic potential, which can be detected in the change of the current flowing through the SQD. Thus we can employ a SQD as a charge sensor for nearby QDs. This is especially useful in configurations where the tunnel barriers are too opaque for the tunnel current to be detected. The sensor has to be in the regime with large  $\mathrm{d}I/\mathrm{d}V_{pg}$  in order to have a large sensitivity, indicated by the working point marked in Fig. 2.7 b.

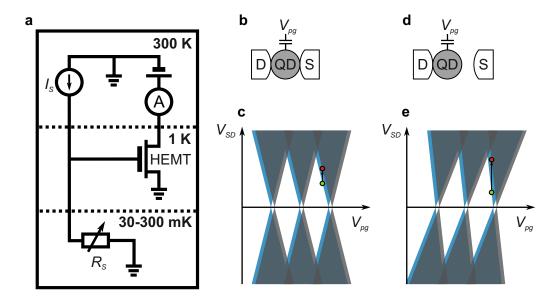

Figure 2.7. – a A schematic illustration of the current through a SQD as a function of the source-drain voltage  $V_{SD}$  and the plunger gate voltage  $V_{pg}$ . The regions with significant current flow are indicated in grey, while the white regions mark the Coulomb diamonds, where current flow is suppressed due to Coulomb interaction. The points marked with the labels (a) to (d) correspond to the configurations depicted in Fig. 2.6. The electron occupation of the SQD, indicated by the labels from (N-1) to (N+2), stays constant inside each Coulomb diamond. b The schematic current I through a SQD as a function of  $V_{pg}$  at the bias voltage indicated by the dotted line in a. Sharp Coulomb peaks emerge where the Coulomb blockade is lifted. Choosing a working point on the side of a peak, as indicated by the circle, the SQD can be used as a charge sensor with a large change in I for a small change in the electrostatic potential.

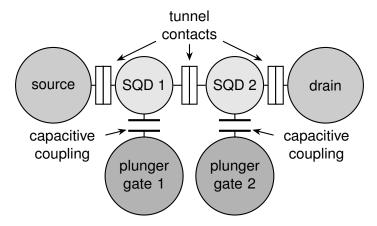

## 2.5. Double quantum dots

For some experiments, such as the demonstration of two-qubit logic or the implementation of singlet-triplet qubits a more complex structure than a SQD is required. Fig 2.8 shows the schematic for a structure with two serial QDs placed in between the reservoirs, with two corresponding plunger gates. In these gate-defined double quantum dots (DQDs), the inter-dot tunnel barrier between the QDs is tunable by

gate voltages, giving the freedom to transition the system from a large SQD to two separated QDs.

**Figure 2.8.** – A schematic illustration of two SQDs connected in series via tunnel contacts forming a DQD. The two separate plunger gates ideally act only capacitively on the corresponding QD.

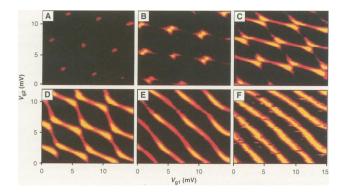

Fig. 2.9 shows the transport current through a serial DQD as a function of the plunger gates of the two QDs for a variation of the inter-dot tunnel coupling. In Fig. 2.9 f the coupling is very large, with the conductance resonances showing one set of parallel lines characteristic for a SQD. Two sets of parallel lines emerge for decreasing tunnel couplings of Fig. 2.9 c-d, indicating the formation of a DQD system, with each set of lines representing the conductance resonances of the individual QDs. For even smaller tunnel coupling, shown in Fig. 2.9 a and b, transport is allowed only at the configurations, where both chemical potentials of the two QDs are aligned with each other and the reservoirs chemical potentials. The points where current can flow in this regime are commonly referred to as triple points, as the charge state of the system sequentially switches between three configurations.

A similar pattern is expected when a charge sensor is employed for the detection of the electron occupation, with two sets of parallel lines emerging in the derivative of the sensor current corresponding to a DQD system.

Figure 2.9. – The current through a DQD as shown in Fig. 2.8 as a function of the plunger gate voltages, here denoted as  $V_{g1}$  and  $V_{g2}$ . The bright values represent a significant current flow, while the dark values indicate a suppressed current flow. The coupling strength increases from A to F. The single set of parallel lines observed in F indicate a SQD. This SQD is split into two separate SQDs forming a DQD when the inter-dot tunnel coupling is decreased by the tuning of a gate voltage, with two sets of parallel lines emerging for a strongly coupled DQD in C-E and triple points being observed for weak inter-dot coupling in A and B. From [53]. Reprinted with permission from AAAS.

## 2.6. Single electron in magnetic field

We now consider a SQD in Si host material which is occupied by a single electron. For zero magnetic field, the single particle ground state is two-fold spin-degenerate. In a non-zero static magnetic field B, the spin-up and -down states  $|\uparrow\rangle$  and  $|\downarrow\rangle$  split by the Zeeman energy splitting

$$E_Z = g_s \hbar \gamma B = g_s \mu_B B \tag{2.24}$$

with

$$\mu_B = \hbar \gamma = \frac{e\hbar}{2m_e}$$

, (2.25)

being the Bohr magneton, the gyromagnetic ratio  $\gamma$  and the electron g-factor  $g_s$ . These states build the basis for the electron spin qubits which will be discussed in the course of this thesis.

# 2.7. Electric dipole spin resonance using a magnetic field gradient

In the following, we will discuss how a magnetic field gradient can be utilized to manipulate single e<sup>-</sup> spins in semiconductor heterostructures. One key requirement for this concept of manipulation is the presence of a small magnet, typically referred to as micro- or nanomagnet, that provides a local magnetic field gradient across the region where the electron is confined.

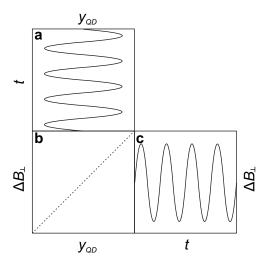

Figure 2.10. – Illustration of artificial spin-orbit coupling: **a** The QD position  $y_{QD}$  as a function of time t. In our device the change in position is induced by a microwave (MW)-pulse applied to a gate near the SQD confining the electron. **b** The field component  $\Delta B_{\perp}$  perpendicular to  $B_{ext}$  as a function of  $y_{QD}$ . **c** The oscillating ac magnetic field perpendicular to  $B_{ext}$  in the electron's rest frame.

For EDSR the magnetic field component  $B_{\perp}$  perpendicular (transversal) to  $\vec{B}_{ext}$  is relevant. Fig. 2.10 a shows as schematic representation of the position of the electron wavefunction center  $y_{QD}$  as a function of time t. This oscillating displacement, in our case, is induced by applying an ac electric field to a gate in proximity of the SQD confining the electron. As illustrated in Fig. 2.10 b the transversal magnetic field gradient  $\Delta B_{\perp}$  converts this oscillation in space into an ac magnetic field perpendicular to  $\vec{B}_{ext}$  in the electrons rest frame, with the resulting oscillation shown in Fig. 2.10 c. This conversion of the electron motion into an ac magnetic field via the artificial spin-orbit coupling introduced by the local magnetic field gradient is the key component for all-electrical spin-manipulation in our <sup>28</sup>Si/SiGe spin-qubit device.

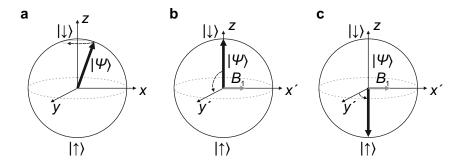

**Figure 2.11.** – Illustration of EDSR on the Bloch sphere with  $|\downarrow\rangle$   $|\uparrow\rangle$  as the basis states for  $|\Psi\rangle = a |\downarrow\rangle + b |\uparrow\rangle$ ;  $a, b \in \mathbb{C}$ : **a** The laboratory frame of reference, where  $|\Psi\rangle$  precesses around the z-axis with  $\omega_L$ . **b** The rotating frame of reference with x', y' rotating at  $\omega_L$  around the z-axis. The ac magnetic field, shown in Fig. 2.10 c, converts into a stationary field  $B_1$  along the x-axis. **c** The spin precesses around the  $B_1$  axis, leading to Rabi oscillations.

Yet, for a controlled spin-manipulation it is required to couple resonantly to the electron spin. The spin precesses around  $\vec{B}_{ext}$  with the Larmor frequency

$$f_L = \frac{\omega_L}{2\pi} = \frac{g\mu_B B}{h},\tag{2.26}$$

where g is the electron g-factor,  $\mu_B$  is the Bohr magneton, B is the total magnetic field along the nanomagnet axis and h is the Planck constant.

Fig. 2.11 a shows a representation of the electron wavefunction  $|\Psi\rangle=a|\downarrow\rangle+b|\uparrow\rangle$ ;  $a,b\in\mathbb{C}$  on the Bloch sphere with the qubit basis states  $|\downarrow\rangle$  and  $|\uparrow\rangle$  located on the poles of the sphere. In this representation the external magnetic field  $B_{ext}$  is oriented along the z-axis. For any  $|\Psi\rangle$  not oriented parallel or anti-parallel to the z-axis,  $|\Psi\rangle$  undergoes a precession around the z-axis at a frequency of  $\omega_L = \frac{g\mu_B B}{h}$ . Fig. 2.11 b shows the reference frame rotating at  $\omega_L$  indicated by the rotating basis vectors x' and y'. The electron is in the ground state  $|\Psi\rangle=|\downarrow\rangle$  represented by the black arrow. The gray arrow represents the effective magnetic field  $B_1$  created by the resonant driving in the nanomagnet gradient, which is stationary in this rotating frame of reference. This stationary field pointing along the x'-axis in turn leads to a precession of  $|\Psi\rangle$  around the x'-axis at a Rabi frequency of  $\omega_{Rabi} = \frac{g\mu_B B_1}{h}$ . The magnitude of  $B_1$  depends on the microwave amplitude, the capacitive coupling of the driving gate onto the QD as well as the strength of the magnetic field gradient. Fig. 2.11 c shows the case where  $|\Psi\rangle$  was rotated by 180° using a microwave pulse of the length  $t_{MW} = \frac{\pi}{\omega_{Rabi}}$  resulting in  $|\Psi\rangle = |\uparrow\rangle$ .

# 3. Gating of undoped Si/SiGe 2DEG

In this chapter, we will discuss the solid-source MBE of the undoped Si/SiGe heterostructures used as the basis for all devices studied in the rest of the thesis. The charge carrier accumulation in these undoped structures will be demonstrated, followed by a characterization in the form of a magnetotransport study. We will focus on the behavior of Hall bar samples when a bias voltage is applied to the accumulation gate during the cool-down and how the sample characteristics change under illumination at cryogenic temperatures. In particular, we will discuss a previously proposed model [40, 54] based on interface trap states to explain the observed illumination behavior.

### 3.1. Growth and semiconductor layer structure

#### 3.1.1. Molecular beam epitaxy

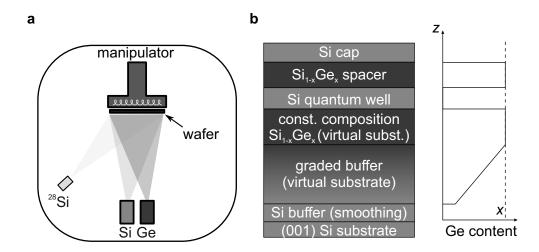

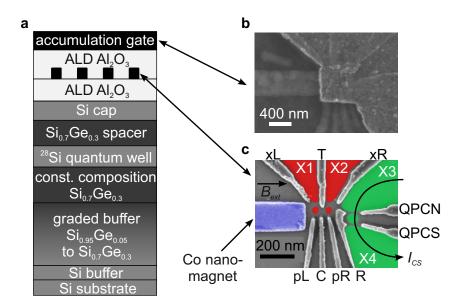

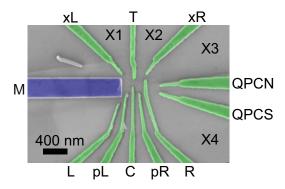

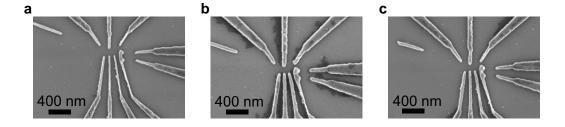

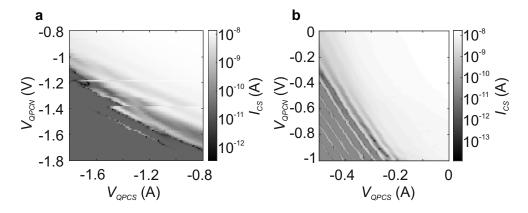

The Si/SiGe heterostructures used for the studies in this thesis were grown by means of solid source MBE based on recipes described in [38–40]. In Fig. 3.1 a the epitaxy chamber is schematically depicted. There are electron beam evaporator sources equipped with single-crystalline natural silicon and germanium, labeled Si and Ge, respectively. A smaller electron beam single-crystalline source equipped with single-crystalline isotopically purified  $^{28}$ Si is located at the side of the chamber. The source crystal for  $^{28}$ Si, provided by the Leibniz-Institut für Kristallzüchtung (IKZ) in Berlin, is purified to a residual concentration below 60 ppm  $^{29}$ Si [34, 35]. The wafer, onto which the heterostructure is grown, is attached to the temperature-controlled manipulator shown at the top. The chamber is pumped to an ultra high vacuum (UHV) base pressure below  $5 \times 10^{-11}$  mbar.

In order to reach relaxed SiGe as a basis for a strained Si QW, a graded buffer is grown onto the initial (001) Si wafer. As shown in Fig. 3.1 b, within the graded buffer, the Ge content x is linearly increased over a thickness of several  $\mu$ m to the desired composition of  $Si_{1-x}Ge_x$ . This gradual increase in Ge content leads to a formation of threading dislocations which tend to stay in regions of constant Ge

Figure 3.1. – a Schematic representation of the MBE ultra high vacuum chamber, including the source cells for Si, Ge and <sup>28</sup>Si. The wafer, colored black, is attached to the temperature controlled manipulator. b Illustration of a typical undoped Si/SiGe layer structure. The Ge content through the layer structure is indicated by the graph on the right and additionally by the tone of the background, with a light gray corresponding to a low Ge content while a dark gray represents a higher Ge content. The Ge content is linearly increased in the graded buffer layer.

content. Therefore, while the relaxation of the lattice is promoted, the dislocation density at the top of the graded buffer is reduced compared to other buffer concepts such as low temperature Si [38]. This graded buffer is followed by a layer of relaxed constant composition SiGe, completing the part of the heterostructure denoted as virtual substrate (VS) in Fig. 3.1 b. A strained Si QW is grown onto the VS. Either natural Si or <sup>28</sup>Si were employed as a QW material in this thesis. A SiGe spacer is grown to keep the QW away from the heterostructure surface, in order to reduce the scattering potential of defects for a 2DEG in the QW. Finally, a Si cap is employed to create a more stable natural oxide, compared to oxidized SiGe. A chemically stable surface protects the 2DEG properties from deterioration over time.

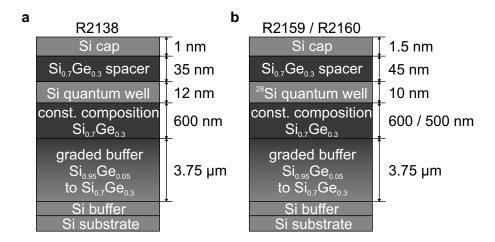

Fig. 3.2 gives a schematic representation of the two layer structures used for all Hall bar samples and QD devices studied in this thesis. Here, Fig. 3.2 a shows a natural Si QW structure with a  $35\,\mathrm{nm}$  Si<sub>0.7</sub>Ge<sub>0.3</sub> spacer and a  $1\,\mathrm{nm}$  Si cap and Fig. 3.2 b shows an isotopically purified <sup>28</sup>Si QW structure with a  $45\,\mathrm{nm}$  Si<sub>0.7</sub>Ge<sub>0.3</sub> spacer and a  $1.5\,\mathrm{nm}$  Si cap.

#### 3.1.2. Post-growth processing

In further ex-situ processing, outside of the ultra high vacuum of the MBE, the ohmic contact to the QW is created by implantation of high energy ions and a rapid thermal activation anneal at a temperature of  $700\,^{\circ}\text{C}$  for  $30\,\text{s}$ , both performed in the group of Kentarou Sawano (Advanced Research Laboratories, Tokyo City University, Tokyo, Japan). An Al<sub>2</sub>O<sub>3</sub> gate oxide is applied by atomic layer deposition (ALD) at  $300\,^{\circ}\text{C}$ . We employ a post-ALD anneal at  $350\,^{\circ}\text{C}$  for  $15\,\text{min}$  in a forming gas environment ( $10\%\,\text{H}_2\,90\%\,\text{N}_2$ ). The bond pads for the ohmic contacts and the metallic gates are patterned by lithography and metallization in a standard evaporation chamber.

**Figure 3.2.** – Layer structures with the layer thicknesses noted on the right: **a** A natural Si QW with 35 nm  $\rm Si_{0.7}Ge_{0.3}$  spacer and 1 nm Si cap (R2138). **b** A  $\rm ^{28}Si$  QW with 45 nm  $\rm Si_{0.7}Ge_{0.3}$  spacer and 1.5 nm Si cap (R2159 and R2160).

#### 3.2. Hall measurement

In this section, we present the methods for the characterization of the Si/SiGe heterostructures studied in this thesis. We start with an overview of the Hall bar sample layout employed to access important heterostructure properties. We will proceed with a short description of the electrical magnetotransport measurement used for the determination of the charge carrier density and mobility throughout this chapter.

#### 3.2.1. Hall bar sample layout

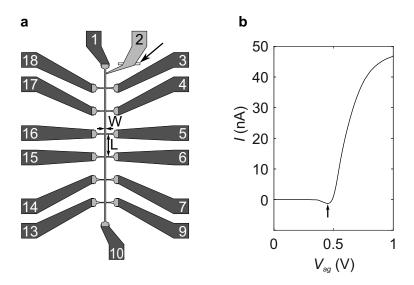

As shown in Fig. 3.3 a, we fabricate gate-induced Hall bars with the accumulation gate depicted in light gray. This gate is employed to induce charge carriers forming a 2DEG in the QW via the field effect. The Hall bar borders are given by the regions where the field induced by the gate is too weak to induce charge carriers in the QW. The individual Hall bar segments have a width-to-length ratio of  $\frac{W}{L} = \frac{1}{15}$  with  $W = 20 \,\mu\text{m}$  and  $L = 300 \,\mu\text{m}$ . The QW is contacted by ion-implanted regions, shown in dark gray in Fig. 3.3 a. An etched bar, indicated by the arrow in Fig. 3.3 a, prevents a leakage current from the accumulation gate bond pad (labeled 2) into the active Hall bar region which has occasionally been observed experimentally.

Figure 3.3. – a Hall bar sample layout, with implanted regions in dark gray, accumulation gate in light gray and an etched leakage current block marked by the arrow. The contact numbers which we will refer to in this chapter are indicated in white. b Current through a Hall bar sample as a function of the accumulation gate voltage  $V_{ag}$ . A significant current flows when a threshold voltage  $V_{thr}$  is reached. The maximum current through the sample is limited to 50 nA by a 100 MΩ resistor. The arrow marks the negative current feature, attributed to a non-linear I-V curve.

#### 3.2.2. Accumulation of charge carriers in undoped Si/SiGe

Using a standard low-frequency lock-in technique, we measure the current through the sample as well as the longitudinal and Hall voltages in a four-point geometry for one or more segments of the gate-induced Hall bar. For details on the measurement setup, see A.2.1. This allows us to calculate  $\rho_{xx}$  and  $\rho_{xy}$ , the longitudinal and transversal resistivities, using the width-to-length ratio of the Hall bar following the Eqs. 2.2 and 2.3 in Sec. 2.3.

Fig. 3.3 b shows the current flowing through a typical Hall bar sample while increasing the accumulation gate voltage  $V_{ag}$  from  $0\,\mathrm{V}$  to  $1\,\mathrm{V}$ . We limit the maximum current flowing through the sample to  $50\,\mathrm{nA}$  by a  $100\,\mathrm{M}\Omega$  series resistor to prevent damaging of the sample by resistive heating. In the regime of  $0\,\mathrm{V} \le V_{ag} \le 0.5\,\mathrm{V}$  there is no significant current flow through the sample, which we attribute to the energy of the first 2D subband  $(E_{1st\ sb})$  in the QW still lying above the Fermi energy  $(E_F)$ . At about  $V_{ag} = 0.5\,\mathrm{V}$ , marked by the arrow in Fig. 3.3 b, we observe a negative current which is a measurement artifact, explained by a non-linear I-V curve exhibited for low densities of charge carriers in the QW causing a rectification of AC noise signals [55]. With increasing  $V_{ag}$   $E_{1st\ sb}$  in the QW gets shifted below  $E_F$ . The current through the sample approaches  $50\,\mathrm{nA}$ , as the 2D charge carrier density in the QW  $(n_{QW})$  increases, as a result of the capacitive coupling of the accumulation gate to the QW.  $V_{ag}$  thus is a tuning knob for the charge carrier density, which will be used to conduct the studies presented in the following sections.

#### 3.2.3. Magnetotransport characterization

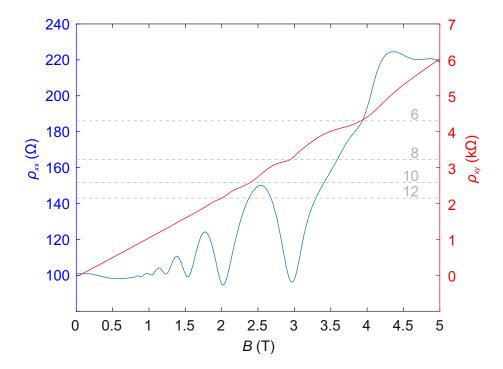

An exemplary magnetotransport measurement on the sample R2160A8 for a constant  $V_{ag} = 1.1 \,\mathrm{V}$  is shown in Fig. 3.4, where we plot  $\rho_{xx}$  and  $\rho_{xy}$  as a function of the external magnetic field B pointing in out-of-plane direction. For low magnetic fields,  $\rho_{xy}$  shows a linear behavior. The slope of  $\rho_{xy}$  allows the determination of the type and density of charge carriers via the theory of the classical Hall effect. As intended, we find the charge carriers to be electrons, with a density of  $n = 5.8 \times 10^{11} \,\mathrm{cm}^{-2}$  according to Eq. 2.5. Additionally, using the  $\rho_{xx}$  value for  $B = 0 \,\mathrm{T}$  and Eq. 2.4, the mobility of the charge carriers may be extracted to a value of  $\mu = 1.1 \times 10^5 \,\mathrm{cm}^2\mathrm{V}^{-1}\mathrm{s}^{-1}$ . The mobility is a measure for the scattering of electrons during their transport through the segment under test. Apart from the classical Hall effect, we observe plateaus in  $\rho_{xy}$  at even filling factors indicated by the dotted lines in Fig. 3.4 and Shubnikov-de Haas (SdH) oscillations in  $\rho_{xx}$  for  $B > 1 \,\mathrm{T}$ . These are features of a 2DEG which is

**Figure 3.4.** – Exemplary magnetotransport measurement on a sample with  $^{28}$ Si QW and 20 nm of  $\text{Al}_2\text{O}_x$  (R2160A8). The longitudinal resistivity  $\rho_{xx}$ , plotted in blue as a function of the magnetic field B, shows Shubnikov-de Haas oscillations indicating a well defined 2DEG. The transverse resistivity  $\rho_{xy}$ , plotted in red as a function of B, shows a linear behaviour for low magnetic field strengths. Quantum Hall plateaus are observed for even filling factors indicating a twofold degeneracy in this measurement.

well described by the theory of the integer quantum Hall effect. The SdH oscillations allow for a separate determination of the charge carrier density, only taking into account charge carriers in the 2DEG. Due to the comparatively larger effective  $e^-$  mass, in contrast to for example the extensively studied GaAs material system, only a few SdH oscillations are observed in our samples in the accessible magnetic field range of  $B < 5\,\mathrm{T}$ . These few oscillations render the determination of the charge carrier density error prone. Therefore, the charge carrier densities presented in this thesis are solely extracted from the classical Hall effect.

# 3.3. Introduction to the gating regimes of undoped Si/SiGe

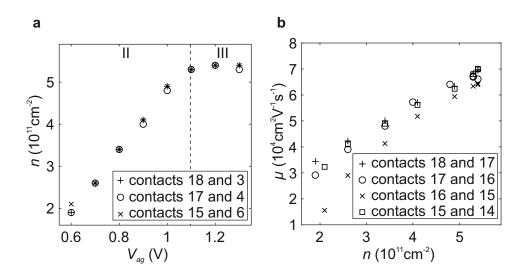

In Fig. 3.5a the electron density n is plotted as a function of  $V_{ag}$  for a Hall bar sample produced from a piece of the wafer R2159 ( $^{28}$ Si QW, see Fig. 3.2b). Note that three different sample positions are plotted. The legend indicates the contact numbers used for the measurements as introduced in Fig. 3.3a. The charge carrier density rises linearly with increasing  $V_{ag}$  in the regime labeled II in Fig. 3.5a, until the saturation regime, labeled III, is reached for  $V_{ag} > 1.1\,\mathrm{V}$ . The linear increase in charge carrier density in regime II is in perfect agreement with a simple plate capacitor model, with the plates being represented by the accumulation gate and the 2DEG [40, 54, 56]. Based on a previously introduced phenomenological model [40], we attribute the saturation to a charge transfer process from the QW to trap states at the semiconductor-insulator interface. As the densities for all contact pairs coincide, we conclude that the density is constant across the  $4\times 5\,\mathrm{mm}^2$  sample for a given  $V_{ag}$ . This behavior is representative for all Hall bar samples ( $\sim 10$ ) studied in the course of this thesis.

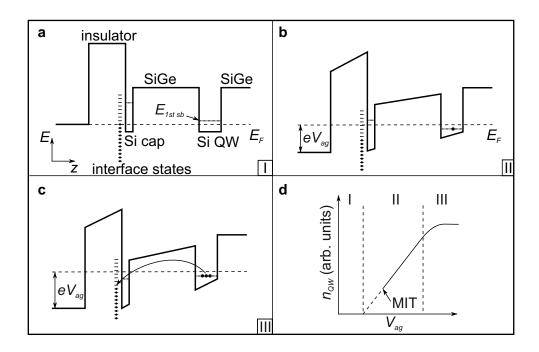

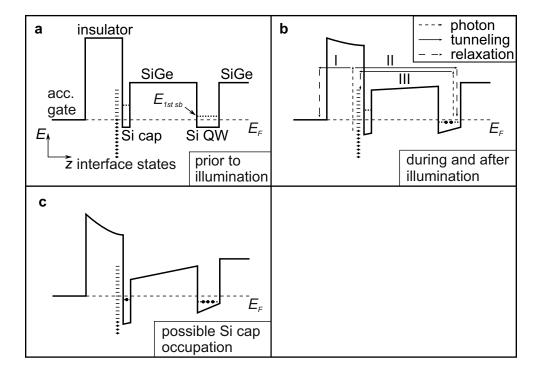

In Fig. 3.6 a-c we give a schematic representation of the conduction band structure for the three regimes proposed in the model, labeled I to III. Fig. 3.6 d shows a sketch of the charge carrier density as a function of  $V_{ag}$  with the regimes separated by the dashed lines. Fig. 3.6 a represents the starting condition for a sample cooled to 1.5 K with a cool-down voltage  $V_{cd} = 0$  V applied to the accumulation gate during cool-down. We sketch the conduction band edge as a function of the z-coordinate (growth direction of the heterostructure). The strained Si-material of the QW and the Si cap form the minima of the conduction band in the heterostructure. Since the heterostructure is undoped, there is no inherent band bending and the ground state energy for electrons in the conduction band  $E_{1st\ sb}$ , indicated by the dotted line in

Figure 3.5. – a Charge carrier densities n extracted at three contact pairs via the classical Hall effect theory as a function of the accumulation gate voltage  $V_{ag}$ . A sample with <sup>28</sup>Si QW and 20 nm of  $\mathrm{Al_2O_x}$  (R2159A4) was used for this measurement. A linear regime is observed for  $V_{ag} \leq 1.1\,\mathrm{V}$  where the charge carrier density in the QW may be described by a classical capacitance model (labeled II). For  $V_{ag} > 1.1\,\mathrm{V}$  we observe a saturation attributed to a charge reconfiguration into the semiconductor-insulator interface (labeled III). b Mobilities  $\mu$  as a function of n calculated for four segments along the sample. The mobility rises with increasing n due to self-screening. The segment with contacts 16 and 15 shows a lower mobility compared to the other segments, which is found to be caused by an imperfection in the sample fabrication present in multiple samples.

Fig. 3.6 a, in the QW is above  $E_F$ , indicated by the dashed line.  $E_{1st\ sb}$  in the thin Si cap (1-1.5 nm) lies higher than in the QW (10 nm). Considering the phenomenological model previously developed in our group [40, 54], we assume trap states to be present in the vicinity of the semiconductor-insulator interface. In our model, these states are initially filled up to  $E_F$  when cooled-down from room temperature. Raising the accumulation voltage  $V_{ag}$  decreases the potential of the accumulation gate in this picture, leading to a band bending analogous to the operation principle of a field effect transistor and lowering  $E_{1st\ sb}$  in the QW with respect to  $E_F$ . We define regime I for all  $V_{ag}$  for which in the QW  $E_{1st\ sb}>E_F$  and therefore with no charge carrier density accumulated in the QW. With a more positive  $V_{aq}$ , it is possible to bend the band structure in a way that  $E_{1st\ sb} \leq E_F$  as sketched in Fig. 3.6 b. A non-zero charge carrier density is accumulated, with the density depending on  $V_{ag}$  as well as on the thickness and dielectric constants of the material between the QW and the accumulation gate, according to a simple parallel plate capacitor model. We define regime II for all  $V_{ag}$  where the  $n_{QW}$  shows a linear dependence on  $V_{ag}$ . In this regime,  $V_{ag}$  serves as a tuning knob for the charge carrier density in the undoped Si/SiGe heterostructures studied in this thesis.

As indicated by the arrow in Fig. 3.6 d, the metal-insulator transition (MIT) is crossed in regime II for  $E_{1st\ sb}\approx E_F$ . The values for the charge carrier density at the MIT observed for samples studied in this thesis in the order of  $2\times 10^{-11}$  cm<sup>-2</sup> (compare Fig. 3.5) do match quite well with the theoretical predictions of  $1.6\times 10^{-11}$  cm<sup>-2</sup> for similar undoped Si/SiGe heterostructures [57].

We observe a distinct transition from the linear regime II to a saturation of  $n_{QW}$  above a certain  $V_{ag} = V_{sat}$ , defined as regime III. The constant density for  $V_{ag} \geq V_{sat}$  is further referred to as saturation density  $(n_{sat})$ . Based on the phenomenological model [40, 54], we attribute this saturation to a charge transfer from the QW to the interface trap states which are energetically available, as sketched in Fig. 3.6 c. The charge transfer has been found to be independent of the SiGe spacer thickness in previous results from our group where  $n_{sat}$  did not change significantly for a variation in the spacer thickness [40]. Therefore, we suspect this charge transfer process to involve Fowler-Nordheim tunneling which is dependent on the strength of the electric field present between the QW and the accumulation gate but independent on the thickness of the tunnel barrier [58–60]. One important aspect differs in our model compared to other models discussed in the literature [59, 60]: our model considers trap states, while other models incorporate a secondary conduction channel located at the semiconductor-insulator interface. The absence of a secondary conduction channel

in our structures, is motivated by findings derived from biased-cooling experiments which will be further discussed in 3.4.

In order to investigate the homogeneity of the sample, we turn towards Fig. 3.5 b which shows the mobility calculated for four different segments as a function of the charge carrier density. As expected, the mobility rises for increasing charge carrier densities due to the effect of self-screening [60–62]. One may note, that all but one segment show an identical increase. The lower mobility for the segment between the contacts 16 and 15 was traced back to an imperfection of the lithography mask, as the mobility of this segment was consistently reduced for multiple samples fabricated in the same batch [63]. We conclude that we observe an excellent homogeneity across a single Hall bar sample covering 1.5 mm of active Hall bar region.

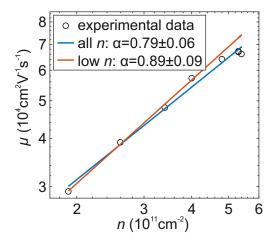

Fig. 3.7 shows a log-log plot of the  $\mu$  vs. n data of contacts 18 and 17 identical to the data shown in Fig. 3.5 b. Assuming a relation of  $\mu \sim n^{\alpha}$  [62], we perform a linear regression to the experimental data and find  $\alpha = 0.79 \pm 0.06$  for the whole data set with  $1.9 \times 10^{11}$  cm<sup>-2</sup>  $\leq n \leq 5.4 \times 10^{11}$  cm<sup>-2</sup> with the fit plotted in blue and  $\alpha = 0.89 \pm 0.09$  for the low densities:  $n \leq 4 \times 10^{11}$  cm<sup>-2</sup> shown in red. Comparing these exponents with the literature [60–62], we exclude interface-roughness scattering to be the dominant scattering mechanism, as it is predicted that the mobility falls with rising charge carrier density in this case [64], which is not the trend that we observe in our samples. Since the exponents for purely background (scattering centers incorporated due to the finite background pressure during growth) and remote impurity scattering (i.e. impurities at the semiconductor oxide interface further discussed in section 3.4.2) in the strong screening regime are predicted to be  $\frac{1}{2}$  and  $\frac{3}{2}$  [62], respectively, it is likely that both of these mechanisms contribute to the scattering in the studied sample. As this analysis features only one data set, it would be worthwhile to extend this study to achieve better statistics.

Figure 3.6. – Schematic representation of the conduction band edge energy as a function of the coordinate in growth direction z draw as a solid line. The ground state energies of electrons in the Si cap and the Si QW are indicated by the dotted lines. a Regime I with  $E_{1st\ sb}{>}E_F$ . b Regime II with  $E_{1st\ sb}{\leq}E_F$ . c Regime III with  $E_{1st\ sb}{\leq}E_F$  and  $V_{ag}\geq V_{sat}$ . The charge transfer from the QW to the interface trap states is indicated by the arrow. d Sketch of  $n_{QW}$  as a function of  $V_{ag}$  with the regimes I to III separated by the dashed lines.

Figure 3.7. – Log-log plot of mobility  $\mu$  as a function of the charge carrier density n. The data points are identical to the segment with contacts 18 and 17 in Fig. 3.5 b. A linear regression to the experimental data yields  $\alpha = 0.79 \pm 0.06$  for the whole data set with  $1.9 \times 10^{11}$  cm<sup>-2</sup>  $\leq n \leq 5.4 \times 10^{11}$  cm<sup>-2</sup> (blue line) and  $\alpha = 0.89 \pm 0.09$  for  $n \leq 4 \times 10^{11}$  cm<sup>-2</sup> (red line).

# 3.4. Biased cool-down

In contrast to a standard cool-down of the sample to a temperature of 1.5 K using a voltage  $V_{cd} = 0$  V applied to the accumulation gate, we may get more insight into the characteristics of the trap states suspected to be present at the semiconductor-insulator interface by examining non-zero cool-down voltages  $V_{cd}$ . Applying non-zero  $V_{ag}$  at room temperature induces internal electric fields in the structure which should influence the population of possible charge traps before cool-down.

#### 3.4.1. Shift of the threshold voltage and density

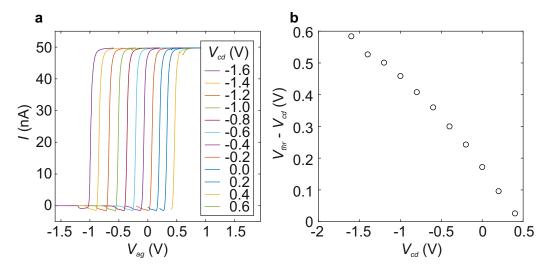

In Fig. 3.8 a, we plot the increasing current through the sample as a function of  $V_{ag}$  applied at 1.5 K after cool-downs with a variety of cool-down voltages  $V_{cd}$  indicated in the legend.  $V_{thr}$  is defined as the voltage where  $I(V_{ag}) = 1 \,\mathrm{nA}$ . We observe a shift in the threshold voltage  $V_{thr}$  as a function of  $V_{cd}$  in the form of a significant x-axis offset of the measured curves. Apart from the shift in  $V_{thr}$ , we observe a typical accumulation curve, as the one previously discussed in Fig. 3.3 b, for most of the tested  $V_{cd}$ . Only towards the two largest  $V_{cd}$ , we see a deviation from the typical behavior: for  $V_{cd} = 0.4 \,\mathrm{V}$  the undershoot feature is not present, while for  $V_{cd} = 0.6 \,\mathrm{V}$  we detect a significant current flowing through the sample even without increasing  $V_{ag}$  for  $V_{ag} = V_{cd}$ .

Figure 3.8. – a Current I through the Hall bar sample (R2138B3) as a function of the accumulation gate voltage  $V_{ag}$  for cool-down voltages  $-1.6 \,\mathrm{V} \leq V_{cd} \leq 0.6 \,\mathrm{V}$  indicated in the legend. b Difference of threshold voltage and cool-down voltage  $V_{thr} - V_{cd}$  as a function of  $V_{cd}$  for the data shown in **a**.  $V_{thr}$  is the voltage where the current through the sample  $I = 1 \,\mathrm{nA}$ .

This shift of  $V_{thr}$  is consistent with the hypothesis of  $V_{cd}$ -dependent change in the charge configuration of trap states at the semiconductor-oxide interface [40, 56]. The  $V_{cd}$  applied to the accumulation gate while the device is cooled to a temperature of 1.5 K sets the interface state occupation for the cool-down, with more negative (positive)  $V_{cd}$  leading to a decrease (increase) in the negative charge at the interface. The interface charge configuration stays constant for  $V_{ag}$  variations at 1.5 K, unless the saturation regime III, introduced in section 3.3, is reached. This leads us to the conclusion, that indeed trap states are involved in the mechanism shifting  $V_{thr}$ , since the trap states are expected to stay at a constant charge configuration for moderate  $V_{ag}$  keeping the system in regimes I and II. In contrast, a secondary conduction channel could be loaded with charge in a similar way for positive  $V_{cd}$ , but we would not expect that the charge in a secondary conduction channel would stay constant, as we observed in the biased cool-down experiments. Additionally, it is hard to imagine why a negative  $V_{cd}$  should induce a  $V_{thr}$  shift involving a secondary conduction channel as the negative voltage should deplete the channel in this case.

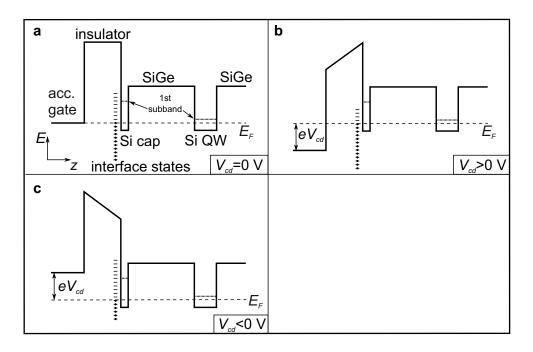

Fig. 3.9 shows a schematic representation of the conduction band edge energy with respect to the growth direction for three regimes of  $V_{cd}$ , reflecting our current understanding of the biased cool-down behaviour. The standard cool-down with  $V_{cd} = 0 \text{ V}$

is depicted in Fig. 3.9 a, while Fig. 3.9 b (c) shows the positively (negatively) biased cool-down cases where the interface trap state occupation is increased (decreased) in comparison to Fig. 3.9 a.

Fig. 3.8 b shows the difference between  $V_{cd}$  and  $V_{thr}$  as a function of  $V_{cd}$  evaluated for the measurements shown in Fig. 3.8 a. Note that we have excluded the data point for  $V_{cd} = 0.6 \,\mathrm{V}$  as the threshold current of 1 nA has already been surpassed at  $V_{ag} = V_{cd}$  for this cool-down voltage. There is a linear regime at  $V_{cd} \approx 0 \,\mathrm{V}$  while  $V_{thr} - V_{cd}$  starts to saturate towards more negative  $V_{cd}$ . The shift of  $V_{thr}$  with varying  $V_{cd}$  is attributed to the compensation of the electric field induced by the accumulation gate through an increased (decreased) density of negative charges at the interface for positive (negative)  $V_{cd}$  [40].

Therefore, we may use  $V_{thr} - V_{cd}$  as a measure for the amount of band bending that is required to induce charge carriers in the QW by increasing  $V_{ag}$ . We expect this measure to depend on the amount of negative charge trapped at the semiconductor-insulator interface, with a larger (smaller)  $V_{thr} - V_{cd}$  corresponding to more (less) negative charges in the interface trap states. The mostly linear dependence of  $V_{thr} - V_{cd}$  on  $V_{cd}$  with a larger  $V_{thr} - V_{cd}$  for more negative  $V_{cd}$  may be explained by an increase in the density of interface trap states loaded at negative  $V_{cd}$  compared to the density at more positive  $V_{cd}$ . More data for an even broader range of  $V_{cd}$  would be beneficial in order to gain insight about the density of the trap states in a larger range of accessible energies. The observed shift in  $V_{thr}$  for all tested  $V_{cd}$  leads us to the conclusion that trap states are present over the entire probed energy range. If the density of trap states would be zero for an energy range accessible by tilting the band structure at room temperature, we would expect to see a saturation in  $V_{thr}$  with respect to  $V_{cd}$ .

Fig. 3.10 a shows the charge carrier density for several  $V_{cd}$  as a function of  $V_{ag}$ . As expected, for each of the curves, the density first increases linearly with increasing  $V_{ag}$  as described by a simple plate capacitor model. For several  $V_{cd}$ , we observe a saturation of the density, denoted regime III in section 3.3. One may note that the charge carrier density obtained at a specific  $V_{ag}$  depends strongly on the chosen cool-down voltage. This effect is explained by a different interface charge occupation for every distinct  $V_{cd}$  leading to a constant electric field influencing the number of charge carriers induced in the QW. One may use this behaviour to engineer a desired charge carrier density at a specified  $V_{ag}$  by varying  $V_{cd}$  accordingly.

**Figure 3.9.** – Schematic illustration of the conduction band edge energy as a function of the coordinate in growth direction z for a variation in  $V_{cd}$ . **a**  $V_{cd} = 0$  V with a flat conduction band edge **b**  $V_{cd} > 0$  V with an increase in interface state occupation compensating for the positive  $V_{cd}$ . **c**  $V_{cd} < 0$  V with a decrease in interface state occupation compensating for the negative  $V_{cd}$ .

#### 3.4.2. Effect of biased cool-down on the mobility

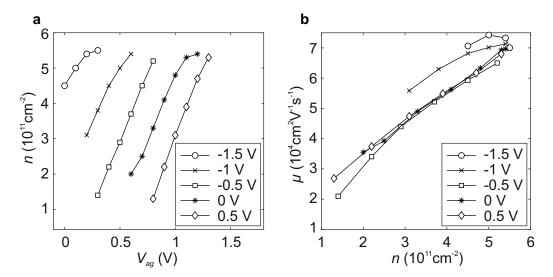

Figure 3.10. – a Charge carrier density n as a function of the accumulation gate voltage  $V_{ag}$  for  $-1.5 \text{ V} \leq V_{cd} \leq 0.5 \text{ V}$  measured at the contacts 17 and 4 (R2159A4). b Mobility  $\mu$  as a function of n for  $-1.5 \text{ V} \leq V_{cd} \leq 0.5 \text{ V}$  measured at the contacts 17 and 16 in the same measurement run as shown in **a**. The lines in between the data points are provided as guides to the eye.

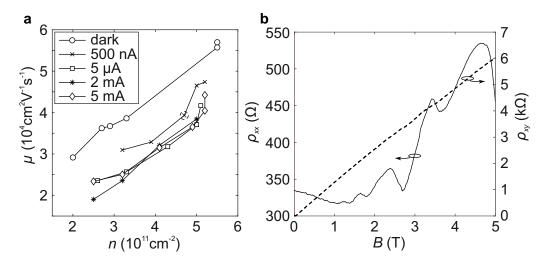

As we attribute the shift in the threshold voltage and the charge carrier densities to a change in the interface state occupation, one might think that the choice of  $V_{cd}$ could have an influence on the mobility of charge carriers as the scattering centers could be either reduced or enhanced by a change in the occupation of interface states. Fig. 3.10 b shows the mobility  $\mu$  as a function of the charge carrier density n for  $V_{cd}$  in the range of  $-1.5\,\mathrm{V} \leq V_{cd} \leq 0.5\,\mathrm{V}$ . For all  $V_{cd}$  the general trend matches the typical behaviour with an increasing mobility for an increasing charge carrier density due to the self-screening of the charge carriers. We observe similar curves for  $-0.5\,\mathrm{V} \le V_{cd} \le 0.5\,\mathrm{V}$  with a maximum mobility  $\mu \sim 6.5 \times 10^4\,\mathrm{cm}^2\mathrm{V}^{-1}\mathrm{s}^{-1}$  at a density of  $n > 5 \times 10^{11} \, \mathrm{cm}^{-2}$ . In contrast, the curves with  $V_{cd} = -1.5 \, \mathrm{V}$  and  $V_{cd} = -1 \,\mathrm{V}$  do show a slightly enhanced mobility at comparable densities. A lower cool-down voltage is associated with a decrease in the number of electrons in the interface trap states after cool-down. This leads us to the conclusion that a decrease in the trap state occupation induced by negative  $V_{cd}$  increases the electron mobility, likely caused by the reduced number of remote impurity scattering centers in the form of charged interface trap states. Note that in the measurement runs with

$V_{cd} = -1.5 \,\mathrm{V}$  and  $V_{cd} = -1 \,\mathrm{V}$  showing the highest mobility, the metal-insulator transition occurs at larger charge carrier densities than the rest of the tested  $V_{cd}$ .

# 3.5. Illumination

The illumination of Si/SiGe samples at low temperatures was previously reported for doped systems with Pd-Schottky gates which were insulating prior to the illumination [65]. It was suspected, that the illumination alters the saturation of Si dangling bonds and the  $E_F$  pinning at the Pd-Si interface. Recently, undoped Si/SiGe heterostructures have been reported to require illumination at cryogenic temperatures in order to measure a significant current through a Coulomb-blockade device [66]. It is still unclear why this illumination does help in making the samples conductive and therefore worth to be investigated in the following section. Furthermore, the influence of this illumination on other sample characteristics such as the mobility is not well understood at the time of the writing of this thesis. In particular, we will show that illumination may be a tool to reset the electrostatic configuration of a sample without requiring the usual thermal cycle.

The cool-down voltage was kept at 0 V for all measurements discussed in this section. The illumination was performed in the cooled-down state at  $T \approx 1.5 \,\mathrm{K}$ , by driving a constant current  $I_{LED}$  for a defined amount of time through a red light-emitting diode (LED) mounted beside the sample. After the illumination, we performed an evaluation of the sample characteristics.

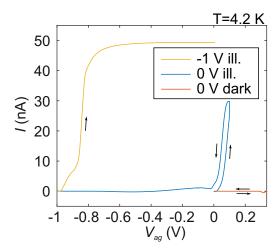

#### 3.5.1. Resetting the charge configuration

In Fig. 3.11 the current through a Hall bar sample (R2159A4) is plotted as a function of  $V_{ag}$  for the dark sample as well as after illumination with a LED for 5 s with a current of 5 mA at  $V_{illum} = V_{ag} = 0$  V and consecutively  $V_{illum} = V_{ag} = -1$  V. Colored in red, the sample shows a region with no significant current flow when  $V_{ag}$  is varied, that is no visible accumulation, for the dark measurement, up to 0.3 V. In contrast, for the measurement taken after illumination at  $V_{illum} = V_{ag} = 0$  V, colored in blue, a significant current flow is now detected immediately after  $V_{ag}$  is only slightly increased from 0 V. Apart from the shifted  $V_{thr}$ , the accumulation curve is similar to a typical dark accumulation measurement (compare Fig. 3.3 b). After the up-sweep of  $V_{ag}$ , we plot the depletion curve for the sweep to -1 V with the current vanishing at  $V_{ag} \approx -0.4$  V. At  $V_{ag} = -1$  V, in depletion, we performed another illumination with the same parameters as above. Again, as shown by the orange

curve, the current set in right after  $V_{ag}$  was increased from  $V_{illum} = V_{ag} = -1 \,\mathrm{V}$ . Without illumination, no current was detectable up to beyond  $V_{aq} = -0.4 \,\mathrm{V}$  which is the threshold observed in the down-sweep of the blue curve. This experimental behavior indicates that the illumination process alters the electrostatic configuration in the sample in such a way that current is then measured for any small increase in  $V_{ag}$ , independently of the value  $V_{illum}$  at which the illumination is carried out. This leads us to the assumption, that under these conditions,  $E_{1st\ sb}$  of the QW matches  $E_F$ , so that a small increase in the band bending via the field effect induced by the accumulation gate always allows a significant current flow, with a charge carrier density above the MIT. The behavior discussed above was observed in a subset of the samples characterized after illumination. Table 3.1 shows the accumulation behavior for the samples tested in the course of this thesis. Two of the four tested samples show the behavior described above while one sample did not show any sign of a shifted  $V_{thr}$  after illumination and one did show a shift to larger  $V_{thr}$ . We will further discuss our understanding of the mechanism underlying the illumination of Si/SiGe samples in the following section.

Figure 3.11. – Current I through the Hall bar sample (R2159A4) as a function of the accumulation gate voltage  $V_{ag}$  after a cool-down at  $V_{cd} = 0$  V for the following sequence: (Red) Sweep  $V_{ag}$  to 0.3 V, sweep  $V_{ag}$  back to 0 V. (Blue) Illuminate with red LED at  $I_{LED} = 5$  mA for 5 s, sweep  $V_{ag}$  to 0.1 V, sweep  $V_{ag}$  down to -1 V. (Orange) Illuminate with red LED at  $I_{LED} = 5$  mA for 5 s, sweep  $V_{ag}$  to 0 V.

| Sample     | $d_{QW}$                          | $d_{spacer}$    | $d_{\mathrm{Al_2O_3}}$ | $V_{thr}$ shift             |

|------------|-----------------------------------|-----------------|------------------------|-----------------------------|

| R2159A4    | $12\mathrm{nm}^{\ 28}\mathrm{Si}$ | $45\mathrm{nm}$ | $20\mathrm{nm}$        | $V_{thr} \approx V_{illum}$ |

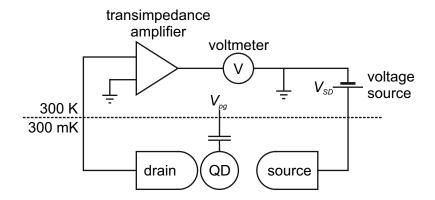

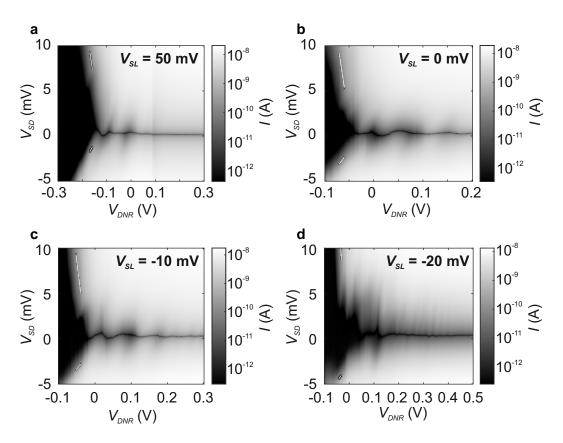

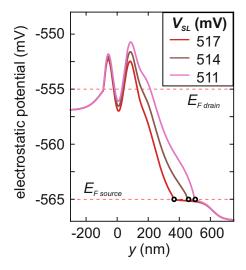

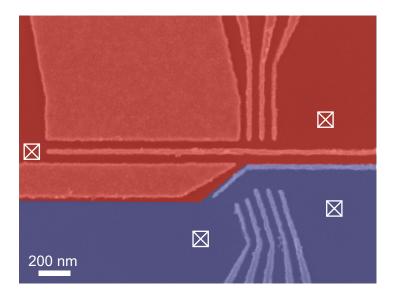

| R2160A5MIV | $12\mathrm{nm}^{-28}\mathrm{Si}$  | $45\mathrm{nm}$ | $100\mathrm{nm}$       | $V_{thr} \approx V_{illum}$ |